JEDEC JESD22B113

O desafio

Os testes mecânicos no nível da placa são um teste de controle de qualidade essencial na indústria de embalagens de microeletrônicas. Eles fornecem dados de teste para apoiar o desempenho dos componentes do IC contra falhas de interconexão durante a remessa e em produtos de uso final, onde são experimentadas tensões cíclicas e choques do impacto.

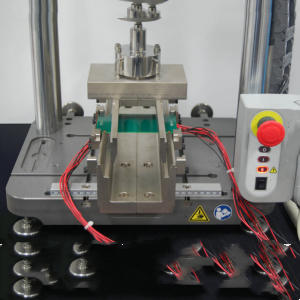

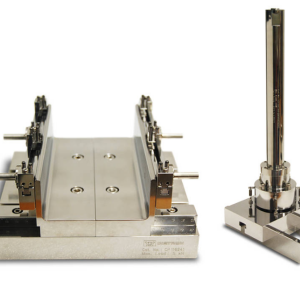

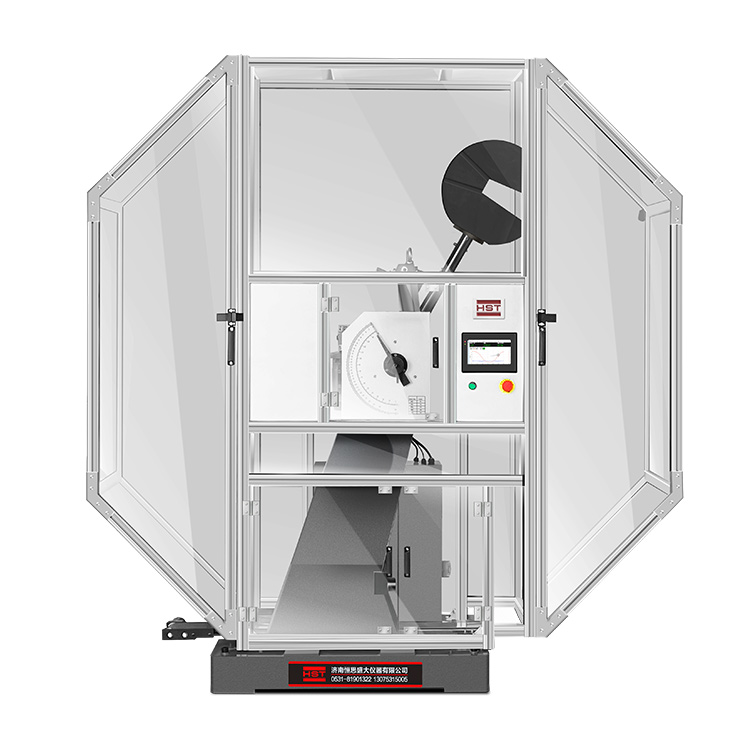

O método de teste JEDEC JESD22B113 é usado para avaliar e comparar o desempenho dos componentes eletrônicos montados na superfície em um ambiente de teste acelerado para aplicações de produtos eletrônicos portáteis. Isso é feito usando um método de teste de flexão cíclica de 4 pontos especificado.

Nossa solução

O padrão recomenda um design de amostra semelhante em tamanho e layout a um teste de impacto em queda. Ele especifica os vãos e a amplitude, frequência e forma de onda cíclicas para executar este teste. A falha de interconexão é determinada com base em cadeias de margarida de resistência, normalmente cinco vezes a resistência inicial ou 1000OHMs, o que for maior. O desafio do teste JEDEC JESD22B113 de que um operador deve ter o sistema de teste gerar continuamente o carregamento da flexão com base em uma forma de onda cíclica especificada na placa de fiação impressa (PWB) por meio da curva de 4 pontos para fadiga de longa data-até 200.000 ciclos em 1-3Hz de frequência sem smotamento de amostragem.